An Overview of Temporary Wafer Bonding Processes

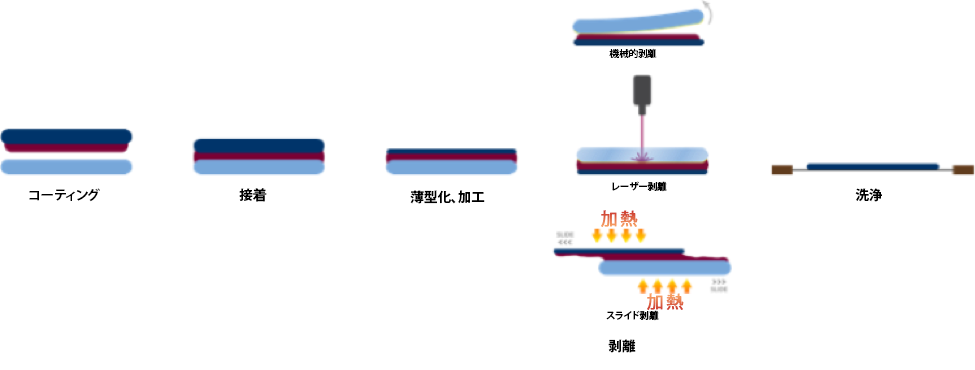

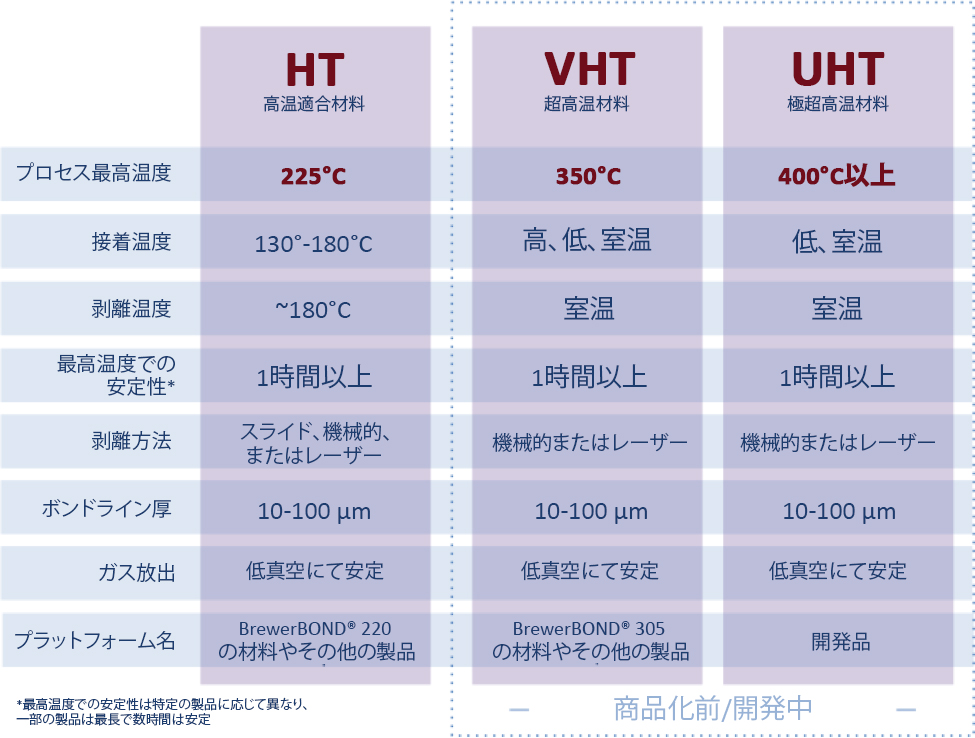

Consumer electronics such as smartphones, tablets, and handheld devices are driving the demand for thinner, smaller, and more highly integrated semiconductor packages. Wafer-level packaging (WLP) is evolving rapidly to shrink package sizes for easier incorporation into mobile electronic devices. Semiconductor die or ‘chip’ sizes have continued to decrease, creating the need for new package designs that provide greater bandwidth and higher pin counts to interconnect the chips. Historically, the packaging industry has relied on flip-chip processing for most WLP applications. Over the last few years many new forms of WLP have been developed to enable higher-density applications, namely fan-out WLP (FOWLP), fan-in wafer-level chip-scale packaging (FI-WLCSP), 3 D FOWLP, 2.5-D integration with interposer technology, and true 3-D IC integration using through-silicon via interconnects. Many of these WLP technologies involve processing of thin wafers that must be mechanically supported during the manufacturing flow. Temporary bonding is proving to be a reliable method for handling and processing thin device wafers. In this method, a device wafer is temporarily adhered to a rigid carrier wafer with a polymeric material. The properties of the polymeric bonding material largely control the stability of the entire structure during thinning and other processing.